两种基于直接数字合成技术的阻抗激励源的对比研究

作者:刘延勇,董秀珍,尤富生,史学涛,季振宇

【关键词】 直接数字合成

Comparative study of two types of exciting sources based on DDS technology

【Abstract】 AIM: To compare the performance of two exciting sources based on direct digital synthesis (DDS) technology and to present some advice for the future system design. METHODS: The exciting source based on DDS chip was designed and was compared with the exciting source based on field programmable gape array (FPGA) chip on the spectrum performance and flexibility. RESULTS: In spectrum performance, there were fewer and smaller stray signals in the FPGA exciting source than that in the exciting source based on DDS chip. In regarding flexibility, the exciting source based on DDS chip was superior. CONCLUSION: The two types of exciting sources have their own advantages and choice should be made by need. As our experiment needs high flexibility, we have chosen the exciting source based on DDS chip.

【Keywords】 direct digital synthesis; exciting source; electrical bioimpedance

【摘要】 目的:比较两种基于直接数字合成技术的阻抗激励源的性能,为以后阻抗系统设计提供指导. 方法:设计了基于直接数字合成(DDS)芯片的阻抗激励源;并且在频谱特性、灵活性等方面与基于可编程逻辑器件(FPGA)芯片的激励源进行了比较. 结果:在频谱特性上,FPGA激励源的信号质量优于DDS芯片激励源. 灵活性上,DDS芯片激励源优于FPGA激励源. 结论:二者各有优缺点,实际应用中,可根据具体情况选择合适的激励源. 我们在实验中对激励源的灵活性要求较高,所以选择了基于AD9850的阻抗激励源.

【关键词】 直接数字合成;激励源;生物电阻抗

0引言

生物电阻抗技术借助置于体表的电极系统向检测对象送入一微小的交流电流或电压,检测相应的电阻抗及其变化情况,以获取人体的生理和病理信息. 在阻抗系统中,激励源是用于产生微小电流或电压信号的单元. 作为阻抗系统的第一级,其激励信号的质量直接影响阻抗测量的准确性;因此系统对激励源的频谱特性、噪声等有较高的要求[1]. 同时,随着多频阻抗技术的兴起,激励源在频率方面的灵活性也越来越重要. 我们比较了两种基于直接数字合成技术的阻抗激励源:一个是我们设计的基于直接数字合成(direct digital synthesis, DDS)芯片的激励源,另一个是课题组设计的基于可编程逻辑器件(field progammable gate array, FPGA)芯片的激励源.

1材料和方法

DDS是根据时钟决定的抽样时间,直接得到正弦信号的抽样值,最后经滤波平滑输出的一种数字频率合成技术[2]. 近年,它的应用越来越广泛. 其工作过程如Fig 1所示.

fo=fc・A/2N(1)

在每个时钟周期内N位相位累加器以频率控制字A为步长进行累加;然后,累加结果的高K位作为地址,在正弦查询表内查表,从而将相位信息转化为M位的正弦幅度值;最后,正弦幅度值经D/A转换和低通滤波,转化为频率为fo的平滑正弦波. 其中fo的公式为:

由公式(1)可得,输出频率fo由相位累加器位数N、参考时钟频率fc和频率控制字A共同决定. 一般情况下,人们主要通过调节频率控制字和参考时钟频率来得到需要的输出频率.

我们设计的阻抗激励源基于DDS芯片AD 9850. AD9850是AD公司推出的直接数字合成波形的专用芯片. 它内部集成了频率字寄存器、相位累加器、正弦查询表、D/A转换器等单元. 能实现全数字编程控制的频率合成. 接上精密时钟源,通过改变芯片频率控制字,AD9850可产生一个频率和相位都可编程控制的模拟正弦波输出. 同时可以通过电阻调节D/A转换器的满量程输出电流;进而控制输出波形的幅值. 设计中AD9850的各参数为:fc=100 MHz,N=32,K=14,M=10. AD9850的合成波形为正弦阶梯波,需要经过低通滤波器平滑滤波,去除频率较高的谐波成分.

用于对比的激励源是本课题组设计的基于FPGA芯片和可编程时钟发生器的系统. 其原理是通过改变时钟频率,达到控制输出频率的目的. FPGA芯片经VHDL语言编程[3],实现相位累加、正弦值查询和时钟控制等功能,其输出经外加的D/A转换器得到正弦信号. 激励源具体参数为:A=1,N=10,K=10,M=12. 输出的正弦阶梯波经过低通滤波器去除高频谐波,得到平滑正弦波.

2结果

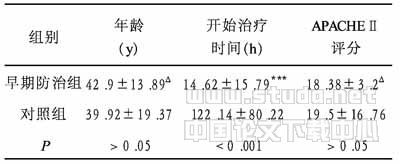

为取得相同的测量条件,两个激励源的低通滤波器均采用基于MAX275的四阶低通滤波器;截止频率为300 kHz. 我们对两种激励源进行对比,从系统的功耗、输出噪声、频率分辨率、频率范围等作了分析. 结果如Tab 1所示.表1两种激励源的主要参数(略)

对比时,系统采用的供电电压为±5 V,负载电阻RL为500 Ω,输出正弦波幅度有效值为1 V. 噪声为复位状态下的噪声峰峰值. 表中FPGA激励源的最小分辨率由选用的可编程时钟控制字、晶振频率和每周期的采样点数决定. DDS芯片激励源的频率分辨率由时钟和频率控制字得到. FPGA激励源的输出频率主要由D/A转换器的速率、FPGA的时钟频率和每周期采样点数决定. AD9850的最高输出频率可达几十兆赫兹[4],但本系统为保证每周期有足够的采样点数,限定最高频率为200 kHz,即每周期采样500点.

同时,我们对两种激励源的输出信号进行了频谱分析. 我们使用NI公司的NI6024E数据采集板,通过虚拟仪器软件LABVIEW 6i编程,实现数据采集、波形显示和频域分析等功能. NI6024E数据采集板有12位的模数转换器,可确保采集信号的精度. 但是NI 6024E数据采集板的最高采样频率为200 kHz,由采样定理可知采集信号的最高频率为100 kHz. 因此,虽然激励源的输出信号的频率可达200 kHz,但是实验中我们只分析了1 kHz~50 kHz的输出信号.

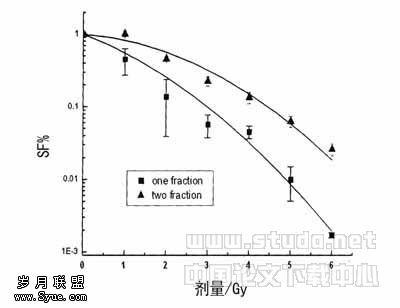

Fig 2和Fig 3分别是两个激励源输出信号波形及频谱分析的结果. 图中,数据采集板的采样速率设置为200 kHz,两个激励源输出信号的频率均为5 kHz. 其中两图中的图A为输出信号的波形,图中每帧显示200点. 图B和图C为频谱分析的结果. 图B为采样点数每组10 000点,频域变换的结果. 为消除随机噪声,突出谐波部分,图C为采样点数每组10 000点,五组数据平均后,进行频域变换的结果.

他频率合成方法相比,它具有频率分辨率高、低相位噪声、频率设置方便、体积小等特点[5]. 本研究中两个DDS激励源各单元进一步集成,比本课题组先前设计的DDS激励源[6]体积更小,频谱、噪声特性更优. 其中,噪声水平由-80 dB降至低于-90 dB,杂散信号最大值由-60 dB降到-70 dB以下. 因此两种激励源均可用于阻抗系统,并且比以前性能有较大提高. 本设计中,两种激励源由于使用的元件及设计思路不同,性能也存在一定的差异:① 从频率设置的灵活性上来讲,基于DDS芯片的阻抗激励源较优. 由于FPGA激励源由参考时钟频率控制输出频率,因此在改变输出频率时,需要由公式(1)得到需要的参考时钟频率,再计算并设置可编程时钟发生器的各控制字;而且设置的同时要保证时钟频率满足时钟发生器的输出条件. 当输出频率变化范围比较大时,设置尤为麻烦. 而DDS芯片激励源只需根据从公式(1)得到的频率控制字进行设置即可[5],简单易行,操作灵活;② 从信号的频谱分析来看,FPGA激励源优于DDS芯片激励源. 从Fig 2和Fig 3的图C可以看出,FPGA激励源的杂散信号主要集中在奇次谐波上,最大值为-77dB. 相对而言,AD9850激励源的杂散信号成分较多,且最大值为-70 dB. 信号质量前者优于后者. 经分析,主要有以下几个原因:首先,FPGA激励源使用的是12位的D/A转换器AD9765,而AD9850内置的D/A转换器为10位. 这使得DDS芯片激励源的幅度量化误差大于前者. 其次,FPGA激励源的输出频率与参考时钟频率的比值始终为2的M次方. 而AD9850的相位累加器是在舍去(N-K)位以后,在正弦查询表中寻址,这将导致DDS芯片激励源的输出频率中含有相位截断误差;再者,FPGA激励源使用的D/A转换器AD9765的性能指标均优于AD9850内置的D/A转换器,这导致DDS芯片激励源因为数模转换的非理想性引起的误差大于FPGA激励源. 虽然AD9850激励源在输出频率为5 kHz时,每周期的采样点数达到214个,远大于FPGA激励源的1024点,但由于以上三个因素,FPGA激励源的频谱特性要优于DDS芯片激励源;③ 其他性能:从性价比和系统功耗上来讲,DDS芯片激励源要优于FPGA激励源. 同时DDS芯片激励源的最小频率分辨率和输出频率范围优于FPGA激励源. 但是由于FPGA激励源是通过VHDL语言实现频率合成,具有可编程的优点. 例如,通过编写分频器可以提高最小分辨率降低最小输出频率;若将每周期采样点数降为512点,最高输出频率也可到160 kHz. 另外,DDS芯片激励源每次只能输出单一频率,可作为扫频模式的多频阻抗激励源和单频模式的阻抗激励源. 而FPGA激励源可根据需要预存不同频率组合的波形抽样值,达到输出多频信号;可实现混频模式的阻抗激励源.

【参考】

[1] 史学涛, 董秀珍, 秦明新,等. 用于电阻抗断层成像的多频波形发生器的设计[J]. 第四军医大学学报,1998;19(增刊):4-6.

Shi XT, Dong XZ, Qin MX, et al. Design of multifrequency waveform generator for electrical impedance tomography [J]. J Fourth Mil Med Univ, 1998; 19(Suppl): 4-6.

[2] 白居宪. 低噪声频率合成[M]. 西安:西安大学出版社,1995:224-230.

[3] 褚振勇,翁木云. FPGA设计及应用[M]. 西安:西安科技大学出版社,2003:219-263.

[4] Analog Devices Inc. CMOS 125 MHz Complete DDS Synthesizer Data Sheet[Z]. 1996.

[5] 高泽溪,高成. 直接数字频率合成器(DDS)及其性能分析[J]. 北京航空航天大学学报,1998;24(5):615-618.

Gao ZX, Gao C. Direct digital synthesis (DDS) and its performance[J]. J Beijing Uni Aeronaut Astronaut, 1998; 24(5): 615-618.

[6] 董秀珍, 史学涛, 秦明新,等. 用于电阻抗参数成像的多频率组合扫频信号源[J]. 第四军医大学学报, 2000;21(11):1367-1370.