内存知识库之内存是如何运作的

来源:岁月联盟

时间:2006-12-14

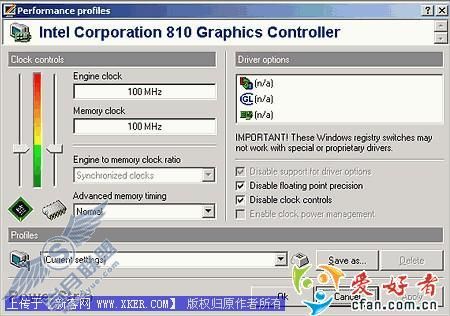

内存控制器 (Memory Controller) 是芯片组的一部分。负责建立内存与中央处理器之间的信息传输。总线是计算机中的数据通路,包括了连接中央处理器,内存以及所有输入输出设备的数种平行电路线。总线的设计或称总线结构,决定数据在主机板速度,依照各部分所需要的传输速度的不同,一个中也有不同种类的总线。

内存总线连接内存控制器与计算机的内存插槽。较新的中内存总线结构包括了一个连接CPU与主存储器的Frontside bus(FSB)以及一个连接内存与L2快速缓冲贮存区的backside bus(BSB)。

内存速度

当中央处理器需要内存中的信息时,它会发出一个由内存控制器所执行的要求,内存控制器接着将要求发送至内存 , 并在信息备妥时向中央处理器报告整个周期,从中央处理器到内存控制器,内存再回到中央处理器所需的时间会因为内存速度以及其它因素而有所不同,例如:总线速度。

内存速度有时以兆赫来计算,或以存取速度来说,送出数据所需的实际时间,以奈秒 (ns) 计算,不管是兆赫或是奈秒,内存速度代表内存模块在收到要求时送出信息的速度。

存取时间 (奈秒)

存取时间从内存模块收到数据要求算起到数据准备完成为止。内存模块标明的存取时间通常在 50ns 到 80ns 的范围中间,在存取时间的计算时, ( 以奈秒计算 ) 数字越小表示速度越快。 举例来说,内存控制器向内存要求数据,内存在 70ns 后作出反应,中央处理器在大约 125 秒后收到信息。所以当使用 70ns 内存模块时从中央处理器下达要求到实际收到信息所需的全部时间为 195ns 。这是因为内存控制器需要时间来处理信息传送并且信息必须从内存模块传送到中央处理器的缘故。

兆赫 (MHz)

由于同步 DRAM 科技,内存芯片能够和计算机的时钟同步,便以兆赫,百万周期 / 秒计算速度更为简易。由于兆赫也被用于计算的其它部分的速度,使得它更容易被用来比较不同组件的速度与同步的功能。为了更清楚了解速度,先了解时钟也显得重要喔。

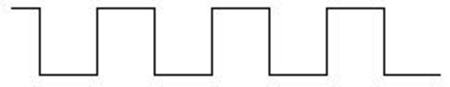

时钟 (System Clock)

时钟装置于主机版上,它像节拍器一样规率性地对计算机的其它部分送出讯号 它的频率通常以方型的波状图形表示 , 如下图:

但是真正的时钟讯号在示波器上显示的图形跟下图比较相似:

近几年来,计算机处理器的速度大幅度的提升,处理器速度的提升提高了计算机的整体性能表现。但是,处理器只是计算机的一部分并且需要依赖其它计算机中的配件来完成作业。由于中央处理器所处理的信息必须从内存中读写,信息在处理器以及内存间的传送速度大幅影响计算机的整体表现。

于是,更快速的内存技术对整体性能表现有重大的贡献,但是,提高内存速度只是解决方案的一部份,信息在处理器以及内存间传送所花的时间通常比处理器执行功能所花的时间更长,这个部分所介绍的技术与改革都是为了提升内存与处理器间数据传输的速度。

快速缓冲贮存内存 (Cache Memory)

快速缓冲贮存区是一个位置非常接近中央处理器的较小容量的高速内存。快速缓冲贮存区是为了向中央处理器供应最常被要求的指令以及数据所设,由于从快速缓冲贮存区取得数据所需时间只是从主存储器取得数据所需时间的数分之一,快速缓冲贮存区的设置能够节省许多时间。

如果所需要的信息并不在快速缓冲贮存区,计算机仍需到主存储器中搜寻,但是由于查询快速缓冲贮存区所需的时间极短,所以仍然是值得的。就如您需要食物时会先检查冰箱是否有需要的食物,因为检查冰箱并不花很多时间。

快速缓冲贮存区依据 “80/20” 规则运作,在计算机的所有的程序信息以及数据里,百分之八十的时候只有百分之二十被使用 ( 这百分之二十可能包括发送或删除电子邮件或将档案储存至硬盘或辨识键盘上被碰触的按键所需要的程序代码 ) 。另一方面,其余的百分之八十的数据被使用的时间只有百分之二十。由于中央处理器正在使用的数据以及指令很可能会被再度使用,设置快速缓冲贮存内存是合理的。

快速缓冲存储器如何运作

快速缓冲存储器就像中央处理器所需要的指示的“排行榜”。内存控制器将中央处理器所要求的所有指令储存在快速缓冲存储器内,每当中央处理器在快速缓冲存储器中找到所需要的数据称为“cache hit”该指令便被提高到“排行榜”的顶端,当快速缓冲存储器已满而中央处理器要求新指令时,便将之取代快速缓冲贮存区中最久未被使用的数据,于是经常使用的最优先数据被保留在快速缓冲存储器而将较不常使用的数据退出。

快速缓冲存储器等级

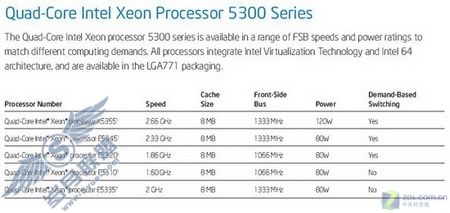

目前大部分的快速缓冲存储器已经被包括在处理器芯片本身当中,但是也有其它的形式;有时可能有置于处理器中的快速缓冲储存内存,在处理器外的主机板上以及靠近中央处理器含有一个快速缓冲贮存内存模块的快速缓冲贮存内存插槽。在每个种类的配置中,每个快速缓冲贮存内存都依与处理器的距离而有等级的不同,举例而言,最靠近处理器的快速缓冲贮存内存称为Level1/L1 Cache ,下一级快速缓冲贮存区称为L2 、L3,并以此类推,除了快速缓冲贮存内存外,计算机通常有其它的快速缓冲储存设备。举例而言,有时便以主存储器做为硬盘的快速缓冲储存区。

您可能会想:既然靠近处理器的快速缓冲存储器这么方便,为何并非所有的主存储器都使用快速缓冲存储器?首先,快速缓冲贮存内存通常使用一种称为 SRAM (Static RAM) 的内存芯片 , 和主存储器所使用的 DRAM相比,它比较昂贵,同时每MB也需要更多空间。并且快速缓冲贮存区只能提高整体性能表现到一定程度,快速缓冲贮存内存的真正利益在于储存最常用的指示。较大的快速缓冲贮存区能够储存较多的数据,但如果这些数据不常被使用,将其至于处理器附近并没有太大利益。

上一篇:路由器和交换机不通的解决方法

下一篇:老鸟献技 DVD刻录机保养之我见