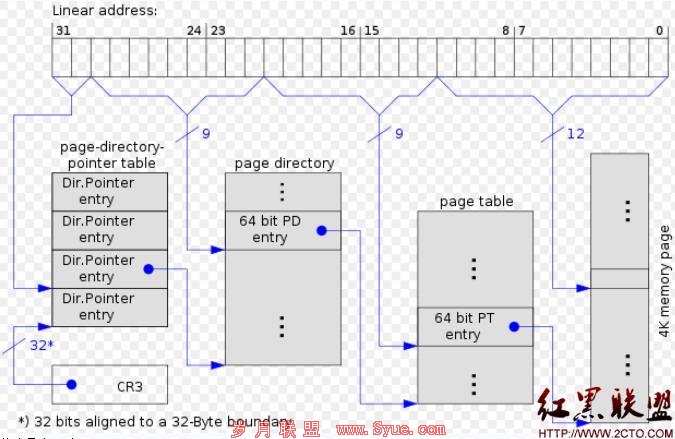

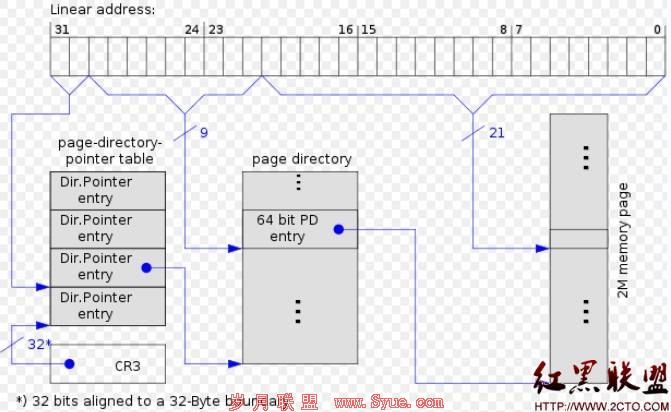

物理地址扩展(PAE)分页机制

来源:岁月联盟

时间:2012-02-19

Intel通过在处理器上把管脚数从32增加到36,以提高处理器的寻址能力,使其达到2^36=64GB,为此,需引入一种新的分页机制。

64GB的RAM被分为2^24个页框,页表项的物理地址字段从20位扩展到24位,每个页表项必须包含12个标志位(固定)和24个物理

地址位(36-12),共36位,因此,每个页表项须从32位扩展到64位(36位>32位,考虑到对齐,因此应将页表项扩大一倍到64位)。

在4KB的常规分页情况下,由于每个页表项大小为64为,因而,原有210大小的页表中,仅能包含512个表项,这占用了32

位线性地址中的9位,同理,由于页目录项与页表项具有同样的结构,高一级的页目录表中也仅能包含512个页表项,同样占用

了32位线性地址中的9位,此时,线性地址剩余位数为:32位(总位数)-12位(页内偏移量)-9位(指示页表中的索引)-9位

(指示页目录表中的索引)=2位,同时,Linux引入了一个页目录指针表(PDPT)的页表新级别,由4个64位表项构成,剩余

的2位即用来指向PDPT中4个项中的一个。

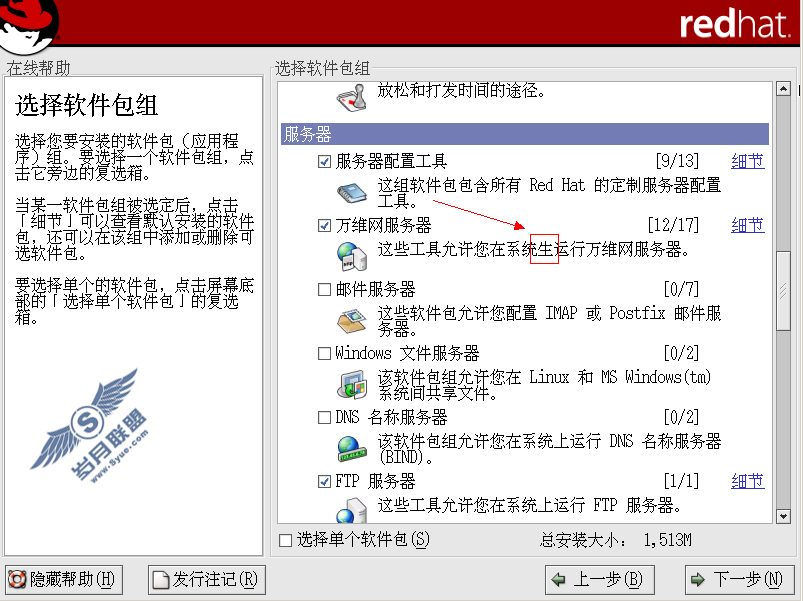

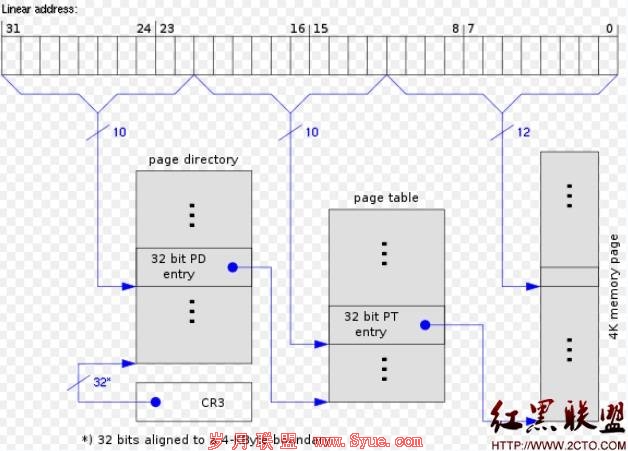

下面4张图详细说明了4种情况下的页表结构(引自Wikipedia)

未启用PAE下的4K分页的页表结构

未启用PAE下的2M分页的页表结构

启用PAE下4K分页的页表结构

启用PAE下2M分页的页表结构