RS系列编译码器的设计与FPGA实现

来源:岁月联盟

时间:2010-08-30

1 引言

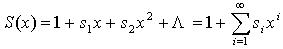

RS码是一种有很强纠错能力的多进制BCH码,也是一类典型的代数几何码。它首先由里德(Reed)和索洛蒙(Solomon)应用MS多项式于1960年构造出来的。它不但可以纠正随机差错,而且对突发错误的纠错能力也很强,因此广泛用于差错控制系统中,以提高数据传输的可靠性。如今,RS(255,223)已被美国航天局和欧洲空间站在太空卫星通信的级联码系统中作为标准的外码以采用。2 RS(255,223)编码器设计

2.1 RS(255,223)编码原理

RS(n,k)码是一种非二进制的BCH码,工程上的RS纠错编码方式为RS(255,223),该码的基本特性如下: ·码类型:系统码,非透明 ·码字长度:每个RS码字中包含n=2J-1=255个RS符号=255×8bit; ·检验位数:n-k=2t ·纠错能力:可纠任一个RS码字中的t=16个RS符号差错; ·码最小距离:dmin=2t+1 ·码的符号:有限域GF(2J)中的元素,每个RS符号由J=8bit构 成,即GF(2)上的8维行向量; ·码字中信息符号数目:k=n-2t=223个; ·码字格式:d1d2d3…di…d223 p1p2…pk…p32,其中di为第i个数据符号,pk为第k个校验符号; ·域生成多项式:有限域GF(28)在其特征域GF(2)上的生成多项式为:F(X)=X8+X4+X3+X2+1 其中F(X)为域生成多项式,X为多项式变量; · 码生成多项式:g(x)=(x+a)(x+a2)...(x+a32) 式中,g(x) 是码生成多项式; ai是GF(a8)中一个元素。2.2 RS(255,223)编码的FPGA实现

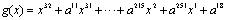

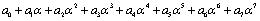

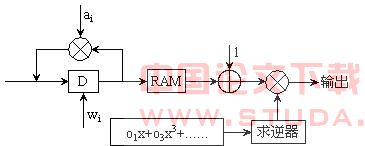

应用Matlab中的符号乘法,得到RS(255,223)生成多项式中的32项乘法系数。结合域生成多项式 生成的监督矩阵表[a0,a1,a2……a254],通过查表得到32项码生成多项式的系数[a18,a251,a215……a11],即 因此,RS(255,223)编码器示意图如图1所示。

因此,RS(255,223)编码器示意图如图1所示。

的线性组合:

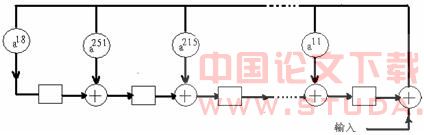

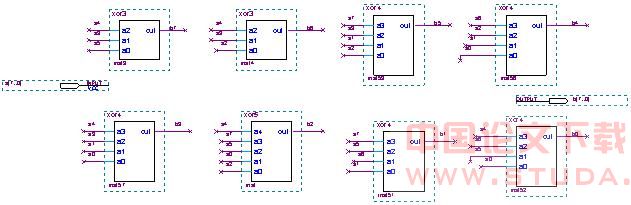

的线性组合: 以乘 a8为例可以表示为: a8(a0+a1a+a2a2+a3a3+a4a4+a5a5+a6a6+a7a7)=a7(a5+a2+a)+a6(a4+a+1)+a5(a7+a2+a+1)+a4(a7+a6+a3+a2+1)+a3(a7+a6+a5+a3)+a2(a6+a5+a4+a2)+a1(a5+a4+a3+a)+a0(a4+a3+a2+1)=a7(a5+a4+a3)+a6(a4+a3+a2)+a5(a7+a3+a2+a1)+a4(a6+a2+a1+a0)+a3(a4+a3+a1+a0)+a2(a7+a5+a4+a2+a0)+a1(a7+a6+a5+a1)+a0(a6+a5+a4+a0) 综上推导,我们可以把所有的乘法器变化为加法器,即模二和的形式。如图2所示。 用输入数据信息实例进行了仿真。即输入信息为0,1,2…222,时,32个校验位输出为102,212,116,164,159,61,229,39,17,244,245,67,253,18,156,217,115,73,31,174,27,140,69,159,104,219,254,187,173,169,10,116。

以乘 a8为例可以表示为: a8(a0+a1a+a2a2+a3a3+a4a4+a5a5+a6a6+a7a7)=a7(a5+a2+a)+a6(a4+a+1)+a5(a7+a2+a+1)+a4(a7+a6+a3+a2+1)+a3(a7+a6+a5+a3)+a2(a6+a5+a4+a2)+a1(a5+a4+a3+a)+a0(a4+a3+a2+1)=a7(a5+a4+a3)+a6(a4+a3+a2)+a5(a7+a3+a2+a1)+a4(a6+a2+a1+a0)+a3(a4+a3+a1+a0)+a2(a7+a5+a4+a2+a0)+a1(a7+a6+a5+a1)+a0(a6+a5+a4+a0) 综上推导,我们可以把所有的乘法器变化为加法器,即模二和的形式。如图2所示。 用输入数据信息实例进行了仿真。即输入信息为0,1,2…222,时,32个校验位输出为102,212,116,164,159,61,229,39,17,244,245,67,253,18,156,217,115,73,31,174,27,140,69,159,104,219,254,187,173,169,10,116。

图2 的加法器表示

3 RS(255,223)译码器设计

、关键方程求解、钱搜索计算错误位置、福尼算法计算错误值。原理[1]-[4]。3.1 伴随式计算

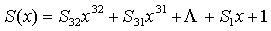

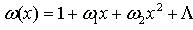

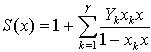

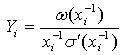

定义伴随多项式为

3.2 关键方程求解

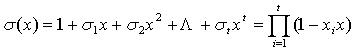

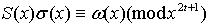

定义错误位置多项式为

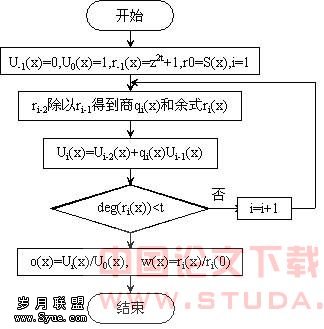

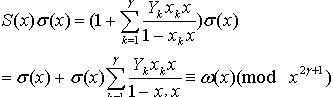

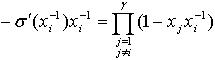

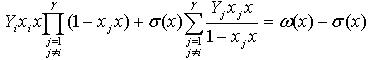

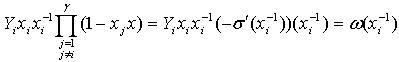

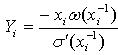

图3 Euclid译码算法流程 RS译码的最后一步就是求错误值Yi。设实际产生的错误个数γ≤t,则

图3 Euclid译码算法流程 RS译码的最后一步就是求错误值Yi。设实际产生的错误个数γ≤t,则

所以

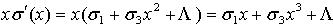

令x= xi-1,则上式成为

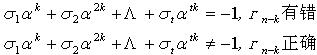

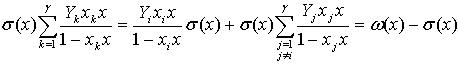

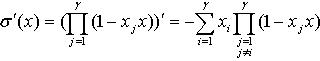

,σ1,σ3……为错误位置多项式奇数项系数

,σ1,σ3……为错误位置多项式奇数项系数3.5 RS(255,223)译码的FPGA实现

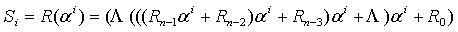

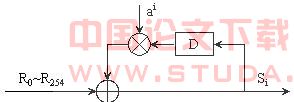

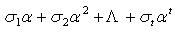

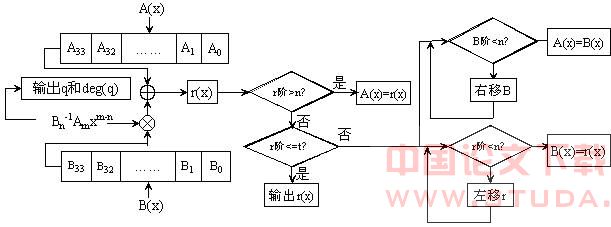

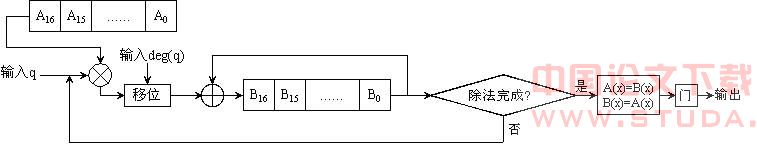

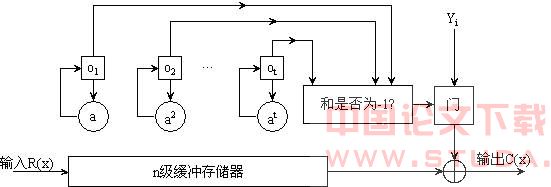

3.5.1伴随式的实现 伴随式计算电路结构如图4所示。图4中R0~R254为译码输入。为了节省硬件资源,同时考虑到每个伴随式系数在计算上相互没有关系,故采用串行计算得到Si。具体做法为:首先将译码输入R0~R254写入到一个片内RAM,每计算一个伴随式,将其从RAM中串行读出,并进行迭代运算。 图4 伴随式计算电路3.5.2关键方程求解的实现 在欧几里德(Euclid)算法[3]中,用到了多项式的除法和乘法运算,为了节省资源,必须利用一个有效的刷新办法对该除法器和乘法器进行实时刷新,使得每进行一次迭代后,除法器和乘法器中的内容及时更新,我们把[3]中的算法结构上做如下的改进:在做多项式除法和乘法之前,先进行数据的并串转换。这样只要一个多项式除法器和一个乘法器就可完成该算法,在保证运算速度的同时也最大限度地节省了硬件资源。在下面的部分给出这两个模块的实现。 1) 多项式除法器 假设多项式A(x)除以B(x)的商为q(x),余数为r(x)。若某次迭代时A(x)的阶数为m,B(x)的阶数为n,m≥n。由多项式除法原理可知,q(x)=Bn-1Amxm-n,每次同m-n一起输出;而r(x)=A(x)-B(x)q(x)是一个降次的过程,每降一次都需要将A(x)用r(x)刷新,直到它的阶数小于B(x)的阶数时,表明此次除法运算结束,用B(x)和r(x)分别对A(x)和B(x)进行同步刷新,继续进行下一次除法运算。当r(x)的阶数小于或等于t时,算法中的除法迭代运算结束。在实现中有两点需要注意:第一点是我们用两组固定长度的寄存器来存放A(x)和B(x)的系数,除了第一次初始化的时候需要给出它们的阶数外,以后每次它们的阶数都是由r(x)或上一次的B(x)的阶数直接赋值,而由于每次r(x)是串行得到的,其阶数能通过判断每次的值是否为零累加得到;第二点是每次在对存放B(x)系数的寄存器进行更新时,应将B(x)的最高位和A(x)的最高位对齐,从而方便r(x)的求解,同时在用B(x)对存放A(x)系数的寄存器进行更新时应注意该操作带来的影响。整个多项式除法器的实现如图5所示。 2) 多项式乘法器 多项式乘法器:将多项式除法运算的结果q和deg(q)实时输入多项式乘法器,A(x)赋初值1,B(x)赋初值0,每完成一次除法运算,多项式除法器模块给此模块一个控制信号,A(x)与B(x)互换。迭代运算时代门关闭,输出无效;当除法迭代结束时,多项式除法器模块的控制信号控制门打开,输出有效。多项式乘法器如图6所示。3.5.3钱搜索计算错误位置的实现在工程上,钱搜索过程可用图7所示的电路实现,它的工作过程如下: (1) t个寄存器寄存σ1,σ2,…,σt,当错误个数γ<t,则σγ+1=σγ+2=…=σt=0。 (2) rn-1正要从缓冲存储器读出之前,t个乘法器由移位脉冲控制乘法运算,且σ1α,σ2α2,…,σtαt存在σ寄存器中,并送入A中进行

图4 伴随式计算电路3.5.2关键方程求解的实现 在欧几里德(Euclid)算法[3]中,用到了多项式的除法和乘法运算,为了节省资源,必须利用一个有效的刷新办法对该除法器和乘法器进行实时刷新,使得每进行一次迭代后,除法器和乘法器中的内容及时更新,我们把[3]中的算法结构上做如下的改进:在做多项式除法和乘法之前,先进行数据的并串转换。这样只要一个多项式除法器和一个乘法器就可完成该算法,在保证运算速度的同时也最大限度地节省了硬件资源。在下面的部分给出这两个模块的实现。 1) 多项式除法器 假设多项式A(x)除以B(x)的商为q(x),余数为r(x)。若某次迭代时A(x)的阶数为m,B(x)的阶数为n,m≥n。由多项式除法原理可知,q(x)=Bn-1Amxm-n,每次同m-n一起输出;而r(x)=A(x)-B(x)q(x)是一个降次的过程,每降一次都需要将A(x)用r(x)刷新,直到它的阶数小于B(x)的阶数时,表明此次除法运算结束,用B(x)和r(x)分别对A(x)和B(x)进行同步刷新,继续进行下一次除法运算。当r(x)的阶数小于或等于t时,算法中的除法迭代运算结束。在实现中有两点需要注意:第一点是我们用两组固定长度的寄存器来存放A(x)和B(x)的系数,除了第一次初始化的时候需要给出它们的阶数外,以后每次它们的阶数都是由r(x)或上一次的B(x)的阶数直接赋值,而由于每次r(x)是串行得到的,其阶数能通过判断每次的值是否为零累加得到;第二点是每次在对存放B(x)系数的寄存器进行更新时,应将B(x)的最高位和A(x)的最高位对齐,从而方便r(x)的求解,同时在用B(x)对存放A(x)系数的寄存器进行更新时应注意该操作带来的影响。整个多项式除法器的实现如图5所示。 2) 多项式乘法器 多项式乘法器:将多项式除法运算的结果q和deg(q)实时输入多项式乘法器,A(x)赋初值1,B(x)赋初值0,每完成一次除法运算,多项式除法器模块给此模块一个控制信号,A(x)与B(x)互换。迭代运算时代门关闭,输出无效;当除法迭代结束时,多项式除法器模块的控制信号控制门打开,输出有效。多项式乘法器如图6所示。3.5.3钱搜索计算错误位置的实现在工程上,钱搜索过程可用图7所示的电路实现,它的工作过程如下: (1) t个寄存器寄存σ1,σ2,…,σt,当错误个数γ<t,则σγ+1=σγ+2=…=σt=0。 (2) rn-1正要从缓冲存储器读出之前,t个乘法器由移位脉冲控制乘法运算,且σ1α,σ2α2,…,σtαt存在σ寄存器中,并送入A中进行 运算和检验。若等于-1,则A输出一个信号,控制门打开,把错误值Yn-1与缓存器输出的rn-1相减,得到rn-1-Yn-1=cn-1。 (3) rn-1译完后,再进行一次相乘,此时σ1α2,σ2(α2)2,…,σt(αt)2存在σ寄存器中,并在A中进行相加运算和检验,对rn-2进行纠错。 (4) 其余码元同(2)一样纠错。

运算和检验。若等于-1,则A输出一个信号,控制门打开,把错误值Yn-1与缓存器输出的rn-1相减,得到rn-1-Yn-1=cn-1。 (3) rn-1译完后,再进行一次相乘,此时σ1α2,σ2(α2)2,…,σt(αt)2存在σ寄存器中,并在A中进行相加运算和检验,对rn-2进行纠错。 (4) 其余码元同(2)一样纠错。

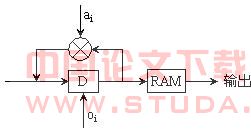

以上的计算是并行计算的,我们在处理中,为了节省硬件资源而采用串行计算,需要把每次迭代的数储存起来,在这里使用了一个片内RAM,实时更新里面的内容,同时RAM的数据地址表示移位次数。当σ1~σ16都移位完成之后,输出RAM数据为0的数据地址即移位次数表示错误位置。改进的串行计算部分电路图如图8所示。

图8 Chien搜索部分电路3.5.4福尼算法计算错误值的实现 福尼算法计算错误值可以采用与钱搜索类似的电路实现。同样,在计算错误值多项式时,我们也采用串行计算,刷新片内RAM并累加得到,整个福尼算法的电路如图9所示。

图8 Chien搜索部分电路3.5.4福尼算法计算错误值的实现 福尼算法计算错误值可以采用与钱搜索类似的电路实现。同样,在计算错误值多项式时,我们也采用串行计算,刷新片内RAM并累加得到,整个福尼算法的电路如图9所示。 图9 福尼算法电路

图9 福尼算法电路4 编解码性能测试与仿真

(1)选取具有代表性的测试数据序列,把编码结果与matlab计算结果比较完全正确。 (2)把编码器与译码器级联,确认译码器输出结果完全正确。 (3)将编码器一组输出码字的任意16位出错作为译码器的输入,经过仿真16位均被纠正。 (4)实现卷积(4,3,3)与RS(255,223)级联,确认输出结果正确。如图10所示,为卷积(4,3,3)与RS(255,223)级联的仿真图。图中rsin为RS编码器输入,rsout为编码器输出,jlianout为RS(255,223) +卷积(4,3,3)级联编码输出,corr_code为RS(255,223) +卷积(4,3,3)级联译码输出。 图10 RS(255,223) +卷积(4,3,3)级联编码输出时序

图10 RS(255,223) +卷积(4,3,3)级联编码输出时序5 FPGA资源分析

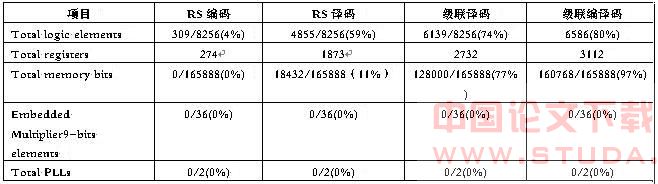

本文RS(255,223)编译码器的设计通过Altera公司的QuartusⅡ软件开发平台上完成了功能仿真、编译综合并优化、布局布线、时序仿真等工作。本文选用CycloneⅡ系列器件的EP2C8T144C8,分别将上述译码器实际占用FPGA资源情况如表1所示。表1 编译码器片内资源占用情况